# Fully transparent field-effect transistor with high drain current and on-off ratio <sup>©</sup>

Cite as: APL Mater. **8**, 011110 (2020); https://doi.org/10.1063/1.5133745 Submitted: 25 October 2019 . Accepted: 02 December 2019 . Published Online: 13 January 2020

Isung Park, I Hanjong Paik, Kazuki Nomoto, Kiyoung Lee, Bo-Eun Park, Benjamin Grisafe, Li-Chen Wang, Sayeef Salahuddin, I Suman Datta, Yongsung Kim, Debdeep Jena, Debdeep Jena, Schlom

### COLLECTIONS

F) This paper was selected as Featured

## **ARTICLES YOU MAY BE INTERESTED IN**

Substrate-orientation dependence of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (100), (010), (001), and ( $\overline{2}01$ ) homoepitaxy by indium-mediated metal-exchange catalyzed molecular beam epitaxy (MEXCAT-MBE) APL Materials **8**, 011107 (2020); https://doi.org/10.1063/1.5135772

Epitaxial integration of high-mobility La-doped BaSnO<sub>3</sub> thin films with silicon APL Materials **7**, 022520 (2019); https://doi.org/10.1063/1.5054810

Adsorption-controlled growth of La-doped BaSnO<sub>3</sub> by molecular-beam epitaxy APL Materials 5, 116107 (2017); https://doi.org/10.1063/1.5001839

APL Mater. 8, 011110 (2020); https://doi.org/10.1063/1.5133745 © 2020 Author(s).

# Fully transparent field-effect transistor with high drain current and on-off ratio

Cite as: APL Mater. 8, 011110 (2020); doi: 10.1063/1.5133745 Submitted: 25 October 2019 • Accepted: 2 December 2019 • Published Online: 13 January 2020

Jisung Park,<sup>1</sup> <sup>(i)</sup> Hanjong Paik,<sup>1,2</sup> <sup>(i)</sup> Kazuki Nomoto,<sup>3</sup> Kiyoung Lee,<sup>4</sup> Bo-Eun Park,<sup>4</sup> Benjamin Grisafe,<sup>5</sup> Li-Chen Wang,<sup>6</sup> Sayeef Salahuddin,<sup>6</sup> Suman Datta,<sup>5</sup> <sup>(i)</sup> Yongsung Kim,<sup>4</sup> Debdeep Jena,<sup>1,3,7</sup> <sup>(i)</sup> Huili Grace Xing,<sup>1,3,7</sup> <sup>(i)</sup> and Darrell G. Schlom<sup>1,7,a</sup> <sup>(i)</sup>

#### **AFFILIATIONS**

<sup>1</sup>Department of Material Science and Engineering, Cornell University, Ithaca, New York 14853, USA

<sup>2</sup>Platform for the Accelerated Realization, Analysis, and Discovery of Interface Materials (PARADIM), Cornell University, Ithaca, New York 14853, USA

<sup>3</sup>School of Electrical and Computer Engineering, Cornell University, Ithaca, New York 14853, USA

<sup>4</sup>Nano Electronics Laboratory, Samsung Advanced Institute of Technology (SAIT), Samsung Electronics, 130 Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do 16678, South Korea

<sup>5</sup>Department of Electrical Engineering, University of Notre Dame, Notre Dame, Indiana 46556, USA

<sup>6</sup>Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, California 94720, USA

<sup>7</sup>Kavli Institute at Cornell for Nanoscale Science, Ithaca, New York 14853, USA

<sup>a)</sup>Author to whom correspondence should be addressed: schlom@cornell.edu

#### ABSTRACT

We report a fully transparent thin-film transistor utilizing a La-doped BaSnO<sub>3</sub> channel layer that provides a drain current of 0.468 mA/ $\mu$ m and an on-off ratio of 1.5 × 10<sup>8</sup>. The La-doped BaSnO<sub>3</sub> channel is grown on a 100–150 nm thick unintentionally doped BaSnO<sub>3</sub> buffer layer on a (001) MgO substrate by molecular-beam epitaxy. Unpatterned channel layers show mobilities of 127–184 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at carrier concentrations in the low to mid 10<sup>19</sup> cm<sup>-3</sup> range. The BaSnO<sub>3</sub> is patterned by reactive ion etching under conditions preserving the high mobility and conductivity. Using this patterning method, a sub-micron-scale thin film transistor exhibiting complete depletion at room temperature is achieved.

© 2020 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/1.5133745

Transparent oxide thin-film transistors (TFTs) have been studied extensively for over a decade for applications that include displays, wearable electronics, and smart windows.<sup>1–3</sup> Due to the relatively high mobilities of the transparent oxide semiconductors used, when scaled to small dimensions, transparent oxide TFTs are expected to have high drain current ( $I_D$ , drain-to-source current per channel width) and low power consumption, which are important for energy-sensitive applications. Tin-based oxide systems are promising materials for transparent oxide TFTs due to the superior oxygen stability and high mobility of these materials at room temperature.<sup>4,5</sup> Among stannates, the transparent perovskite BaSnO<sub>3</sub> is attracting worldwide attention following the recent discovery that La-doped BaSnO<sub>3</sub> has both high mobility at room temperature and excellent oxygen stability. Mobilities as high as 320 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 183 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> have been achieved in Ladoped BaSnO<sub>3</sub> single crystals<sup>4</sup> and epitaxial thin films,<sup>6</sup> respectively, at room temperature. The high mobility of BaSnO<sub>3</sub> is attributed to the small effective mass originating from the large dispersion of the conduction band from the Sn 5*s* orbital,<sup>7</sup> high dielectric constant ( $K \approx 20$ )<sup>8</sup> which reduces dopant scattering,<sup>4</sup> and small phonon scattering.<sup>9</sup>

The performance of TFTs based on BaSnO<sub>3</sub> has been steadily improving in recent years, with the highest  $I_D$  achieved being 0.021 mA/ $\mu$ m.<sup>10</sup> This performance is limited by the large size of the BaSnO<sub>3</sub>-based TFTs, which have channel dimensions of 100–200  $\mu$ m. These large devices have been patterned using metal shadow masks during growth, i.e., without photolithography. Attempts to use photolithography to define smaller devices have been plagued by the creation of oxygen vacancies in the BaSnO<sub>3</sub> film, including the undoped BaSnO<sub>3</sub> buffer layer, during the ion-milling process. These vacancies make the undoped BaSnO<sub>3</sub> buffer layer conductive, shunt the device, and degrade performance.<sup>11</sup> This problem is well known in other oxides as well.<sup>12</sup>

Here, we report growth of high mobility La-doped BaSnO<sub>3</sub> thin films on MgO substrates using molecular-beam epitaxy and use reactive ion etching (RIE) to pattern BaSnO<sub>3</sub>-based TFTs. With appropriate conditions, this etching technique enables BaSnO<sub>3</sub> to be etched with a controllable etch rate while preserving surface roughness and electrical properties including conductivity and mobility. The resulting micrometer-scale photolithography defined BaSnO<sub>3</sub>-based transparent TFT has a peak field-effect mobility of 17.2 cm<sup>2</sup>/V<sup>-1</sup> s<sup>-1</sup>, an on-off ratio over 1.5 × 10<sup>8</sup>,  $I_D$  over 0.468 mA/ $\mu$ m, and a peak transconductance ( $g_m$ ) of 30.5 mS/mm. As we describe below, this is one of the highest performance fully transparent oxide TFTs ever reported.

Epitaxial La-doped BaSnO<sub>3</sub> films were grown on (001) MgO substrates by adsorption-controlled growth using molecular-beam epitaxy with barium, lanthanum, and SnO<sub>2</sub> sources. The details of the growth process are given elsewhere.<sup>6</sup> Epitaxial growth of single-phase La-doped BaSnO3 on MgO substrates was confirmed by x-ray diffraction (XRD) measurements; the full width at half maximum of the BaSnO3 002 peak is 0.31° (see Fig. S1 of the supplementary material). MgO substrates, with a bandgap of about 7.8 eV,<sup>13</sup> are used to avoid the potential complications of persistent photoconductivity from the substrate arising from light exposure during the photolithography process.<sup>14</sup> On the MgO substrate, an undoped BaSnO3 layer followed by a La-doped BaSnO3 layer is grown to form the channel of the TFT as is typical for BaSnO<sub>3</sub>-based TFTs.<sup>10,15–19</sup> The purpose of the undoped BaSnO<sub>3</sub> layer is to reduce the density of threading dislocations that propagate into the overlying doped (and conducting) BaSnO<sub>3</sub>. Even with such a buffer layer, the threading dislocation density of BaSnO3 films grown on MgO as well as other commonly used substrates is of order  $10^{11}$  cm<sup>-2</sup>; an ideal substrate for BaSnO3 has yet to be demonstrated, but several lattice matched candidates are being developed.<sup>2</sup>

The heterostructures for TFTs fabrication consist of a 100-150 nm thick unintentionally doped BaSnO3 buffer layer followed by about 10 nm of La-doped BaSnO<sub>3</sub>. In test structures, the Hall mobility of a 10-nm-thick La-doped BaSnO3 layer (grown on an MgO substrate with an undoped BaSnO<sub>3</sub> buffer layer) reaches 184 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at a carrier concentration of  $6.5 \times 10^{19}$  cm<sup>-3</sup>. Despite the thin La-doped BaSnO<sub>3</sub> film and the use of a nonperovskite MgO substrate, this value is the highest mobility reported for BaSnO<sub>3</sub> thin films; it is slightly higher than the previous record achieved on a DyScO<sub>3</sub> substrate.<sup>6</sup> The Hall mobility of a 10-nm thick La-doped BaSnO<sub>3</sub> layer (on a 150 nm thick undoped BaSnO<sub>3</sub> buffer layer) with a carrier concentration of  $1.3 \times 10^{19}$  cm<sup>-3</sup> is over 90 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. This decrease in mobility as the carrier concentration in La-doped BaSnO3 is reduced below about  $7 \times 10^{19} \text{ cm}^{-3}$  is typical of  $BaSnO_3$  films<sup>6,15,20</sup> and is a result of scattering from the huge density of threading dislocations, which become less effectively screened from the mobile charge carriers as the carrier concentration is reduced.<sup>4,20</sup> The mobility, limited by the threading dislocations, is given by<sup>24,25</sup>

$$\mu_{\rm td} = \frac{4ec^2}{Z^2 \hbar N_{\rm td}} \left(\frac{3n}{\pi^4}\right)^{2/3} (1+y(n))^{3/2},$$

where

$$y(n) = \frac{2\pi^2 \hbar \varepsilon}{e^2 m^*} \left(3\pi^2 n\right)^{1/3}$$

and *e*, *c*, *Z*,  $N_{td}$ , *n*,  $\varepsilon$ , and  $m^*$  are the electron charge, *c*-axis lattice parameter, charge state of a unit cell in a threading dislocation, density of threading dislocations, carrier concentration, dielectric permittivity, and effective mass, respectively. The fitting parameters are given in the supplementary material. The fitting achieved using this formula is overall in good agreement with the experimental data (see Fig. S6 of the supplementary material). The mobilities of our La-doped BaSnO<sub>3</sub> films on MgO are the highest yet reported at the relatively low carrier concentrations and low thickness of La-doped BaSnO<sub>3</sub> layers,<sup>4,15,26,27</sup> which are needed to be able to fully deplete the TFT channel when a voltage is applied to the gate.

In order to make micrometer scale TFTs, it is critical to be able to lithographically pattern the high mobility La-doped BaSnO<sub>3</sub> channel layer without degrading its electrical performance. A few methods have been used in the past to pattern a La-doped BaSnO<sub>3</sub> channel layer. Early BaSnO3 TFTs used shadow masks to define the channel structure during deposition.<sup>10,15–19</sup> This method can pattern the La-doped BaSnO3 layer without degrading its surface roughness and electrical properties, but the channel length is limited to about 100  $\mu$ m. More recently ion-milling has been employed to pattern the La-doped BaSnO3 layer. Although ion-milling can etch La-doped BaSnO3 to micrometer scale dimensions with controllable etch rate, the size of the channel length reported was about 100  $\mu$ m.<sup>11</sup> Importantly, the resulting BaSnO3 TFT with an undoped BaSnO3 layer could not be depleted at room temperature and its on-off ratio was only 2. The reason for the inability to deplete the TFT at room temperature was attributed to significant charge trapping,<sup>11</sup> but our own experiments reveal that undoped BaSnO3 becomes conductive when subjected to ion-milling. The conductivity of an undoped BaSnO<sub>3</sub> layer increased more than 10<sup>8</sup> times following ion-milling even when we use the smallest available acceleration voltage of our equipment, 400 V. Such an enhancement in conductivity of the undoped BaSnO<sub>3</sub> layer is consistent with it is being caused by the creation of oxygen vacancies from the high energy bombardment of Ar ions during the ion-milling process, as has been reported for SrTiO<sub>3</sub>.

The undesired conductance enhancement in unintentionally doped BaSnO<sub>3</sub> resulting from ion-milling can be reduced by annealing the sample in flowing oxygen at temperatures of about 800 °C, but even after such aggressive annealing, the conductance does not fully return to its original state. The effect of annealing on ion-milled undoped BaSnO<sub>3</sub> in flowing O<sub>2</sub> at temperatures from 300 °C to 800 °C is given in the supplementary material (see Fig. S7 of the supplementary material). Therefore, we believe that the conductance of the underlying undoped BaSnO<sub>3</sub> buffer layer caused by the ion-milling process is partially responsible for the poor room-temperature performance of the prior BaSnO<sub>3</sub>-based TFT device subjected to ion-milling.<sup>11</sup> Ion-milling can also alter film stoichiometry and lead to charge trapping from defects along the side walls. For this reason, we have developed an alternate etching process to pattern the BaSnO<sub>3</sub> layers into a TFT.

In order to overcome the limitations of previous techniques used to define BaSnO<sub>3</sub>-based TFTs, we employ reactive-ion etching (RIE) using chlorine and argon gases to etch the BaSnO<sub>3</sub> epitaxial stack. By using a reactive gas such as chlorine, the RIE technique can etch a BaSnO<sub>3</sub> film with a chemical process rather than a purely physical process, in contrast to ion-milling. Under appropriate conditions, the undoped BaSnO3 film conductivity issue that we ascribe to the creation of oxygen vacancies can be resolved. Furthermore, with RIE, we are able to achieve a controllable etch rate that is not dependent on sample quality. In short, our RIE etching process for BaSnO<sub>3</sub> provides a controllable etch rate while preserving surface roughness and electrical properties including conductivity and mobility-qualities critical to the fabrication of high-performance TFTs. BCl3 gas can also be used for RIE etching of BaSnO3 while preserving surface roughness and electrical properties including conductivity and mobility, but the etch rate is lower than when chlorine gas is used. Therefore, using chlorine gas without adding BCl3 gas is preferable. A higher etch rate is desirable to reduce etch time, but there is a trade-off between the etch rate and damage to the BaSnO<sub>3</sub> film. In making the TFTs, the etch rate has been maximized without damaging the properties of the BaSnO<sub>3</sub> film by adjusting RIE etching parameters. The RF power of the RIE is around 80-120 W with a DC voltage in the 200-250 V range. The total gas pressure is around 1-2 mTorr, and a gas ratio between 1:5 and 5:1 is used for the Cl<sub>2</sub> and Ar gases.<sup>2</sup>

The device patterning and fabrication process was completed in the cleanroom environment of Cornell's NanoScale Science and Technology Facility (CNF), except for the atomic layer deposition (ALD) process. For light exposure during photolithography, an Autostep 200 stepper was used. The channel layer was etched using a PT720/740 RIE etching tool. For device isolation, the channel layer was etched down about 18 nm, considerably beyond the 10 nm thickness of the La-doped BaSnO<sub>3</sub> top layer and well into the undoped BaSnO<sub>3</sub> buffer layer. After the etching process, indium tin oxide (ITO) was deposited as source and drain contacts using a PVD75 sputtering tool. The source and drain contacts were patterned by lift-off. A blanket HfO2 gate dielectric layer was then deposited over the full structure by atomic-layer deposition (ALD), at 300 °C with ozone as an oxidant, which leads to have a deposition rate of 0.8 Å/cycle. The thickness of the HfO<sub>2</sub> layer was 20 nm. To complete the TFT, ITO was deposited again on the gate dielectric to form the gate electrode using the same sputtering tool as used earlier in the process. The gate contact was also patterned by lift-off. Electrical measurements were performed using a Cascade probe station with a Keithley 4200 SCS system. All device measurements presented were measured at room temperature in ambient air.

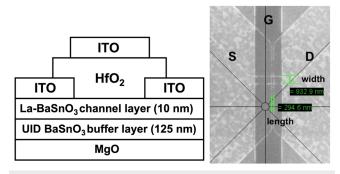

Figure 1 shows a schematic of the BaSnO<sub>3</sub>-based TFT measured in Figs. 2 and 3, together with a scanning electron microscope image of the fully patterned device. The mobility and carrier concentration of the as-grown La-doped BaSnO<sub>3</sub> channel layer in this sample are  $\mu = 65.2$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $n = 1.81 \times 10^{19}$  cm<sup>-3</sup>, respectively, from Hall measurements at room temperature. The channel length and width of the TFT are  $L = 0.3 \,\mu$ m and  $W = 0.93 \,\mu$ m, respectively. This is the smallest BaSnO<sub>3</sub>-based TFT yet reported.<sup>10,11,15-19</sup> Further scaling is limited by the resolution of the light exposing tool.

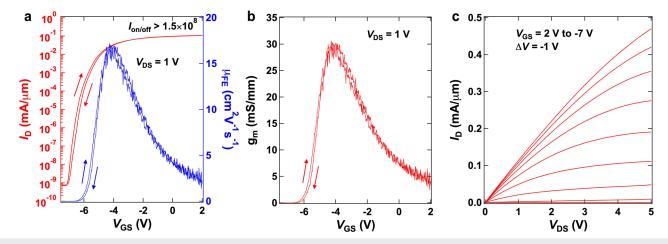

The characteristic curves of the BaSnO<sub>3</sub> TFT are shown in Fig. 2. Figure 2(a) shows the transfer characteristic of the device:  $I_{\rm D}$  vs  $V_{\rm GS}$  (gate-to-source voltage) and  $\mu_{\rm FE}$  (field-effect mobility)

FIG. 1. Schematic and scanning electron microscope image of the BaSnO<sub>3</sub> TFT device. The channel is 0.3  $\mu$ m long and 0.93  $\mu$ m wide.

vs  $V_{GS}$ . As shown in Fig. 2(a), the TFT can be depleted completely at room temperature-a first for a photolithographically defined BaSnO<sub>3</sub>-based TFT.<sup>11</sup> The field-effect mobility of the device is calculated from the relation  $\mu_{FE} = \left(\frac{L}{C_{ox}WV_{DS}}\right) \frac{\partial I_{DS}}{\partial V_{GS}}$ .<sup>30</sup>  $I_{DS}$ , L,  $C_{ox}$ , and W are the drain-to-source current, the channel length, the capacitance of the gate dielectric per unit area, and the channel width, respectively. The capacitance of the HfO2 gate dielectric was measured as shown in Fig. S9 of the supplementary material with a metal-oxide semiconductor (MOS) structure with dimensions 50  $\mu$ m × 50  $\mu$ m. This MOS capacitor has the same La-doped BaSnO3 channel layer and the same ITO gate electrode as the TFT, i.e., the layers measured in the MOS capacitor were deposited on the MgO wafer and patterned into the MOS capacitor test structure and into the TFT. For calculating  $\mu_{FE}$ , the maximum  $C_{ox}$  at the given voltage range has been used so as to not overestimate  $\mu_{FE}$ . The calculated  $\mu_{FE}$  is 17.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The large difference between the field-effect mobility and the Hall mobility can be attributed to the contact resistance. The contact resistance includes the sheet resistance of the ITO contact layer and interface resistance between the ITO contact layer and the La-doped BaSnO<sub>3</sub> channel layer. In the supplementary material (see Fig. S10), we utilize the measured value of the contact resistance to calculate the field-effect mobility; the result is 72 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, which is comparable to the Hall mobility of the as-grown channel layer. From the details of this calculation, it is clear that the high contact resistance is significantly limiting the TFT performance; a lower resistance contact will increase the field-effect mobility and thus the drain current. There is dispersion in the capacitance at measurement frequencies higher than 100 kHz, and it is believed to be related to the trapping of charge by defects or impurities within the HfO<sub>2</sub> film and at the interface between the HfO2 and La-doped BaSnO3 channel layer since the cutoff frequency is 51.6 MHz. The cutoff frequency is cal-culated from the relation  $f = \frac{1}{2\pi RC}$  and is much higher than 100 kHz. The on-off ratio is over  $1.5 \times 10^8$ . This is the highest on-off ratio among BaSnO3 TFTs when an undoped BaSnO3 buffer layer is used.<sup>10,11,7</sup> <sup>18</sup> The subthreshold swing has been calculated from the equation  $S = \left(\frac{\partial \log I_{DS}}{\partial V_{cS}}\right)^{-1}$ , and *S* is 0.15 V dec<sup>-1</sup>. Figure 2(b) shows the transconductance of the device at  $V_{DS} = 1$  V as a function of  $V_{\text{GS}}$ . The transconductance is calculated from the relation  $g_m = \frac{\partial I_{\text{DS}}}{\partial V_{\text{GS}}}$ . The maximum transconductance is 30.5 mS/mm

**FIG. 2.** (a) The transfer characteristic of the TFT based on La-doped BaSnO<sub>3</sub> at  $V_{DS} = 1$  V and the field-effect mobility. The peak field-effect mobility is 17.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and the on-off ratio is over  $1.5 \times 10^8$ . The subthreshold swing is 0.15 V dec<sup>-1</sup>. (b) Transconductance of the device at  $V_{DS} = 1$  V. The maximum transconductance is 30.5 mS/mm. (c) The output characteristic of the device at  $V_{GS} = 2$ , 1, 0, -1, -2, -3, -4, -5, -6, -7 V. The maximum drain current exceeds 0.467 mA/ $\mu$ m.

at  $V_{\rm DS} = 1$  V. This is much higher than the previous record transconductance in a BaSnO<sub>3</sub> based TFT, which is only 2 mS/mm.<sup>11</sup> Figure 2(c) shows the output characteristic of the device, which is  $I_{\rm D}$ vs  $V_{\rm DS}$  (drain-to-source voltage) by varying  $V_{\rm GS}$  from 2 to -7 V. As shown in Fig. 2(c), the drain current reaches over 0.468 mA/ $\mu$ m. The slow increase in the drain current with respect to  $V_{\rm DS}$  is attributed to the high contact resistance. The resistance of the ITO/La-doped BaSnO<sub>3</sub>/ITO channel structure vs channel length is plotted in Fig. S10 of the supplementary material. The source/drain contact resistance between the ITO contact layer and the Ladoped BaSnO<sub>3</sub> channel layer, which is 5.1 k $\Omega$   $\mu$ m, is calculated by

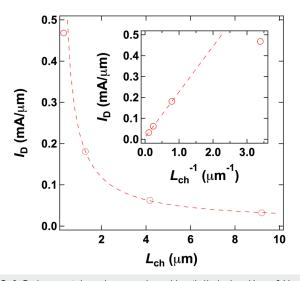

**FIG. 3.** Drain current dependence on channel length ( $L_{ch}$ ) when  $V_{GS} = 2$  V and  $V_{DS} = 5$  V. The drain current ( $I_D$ ) is inversely proportional to the overall channel length except at the shortest channel length, showing little degradation with respect to device scaling. The deviation from linear behavior in the inset at the shortest channel length is likely due to the contact resistance and not short channel effects such as velocity saturation.

extrapolating a linear fit to the plot. The high contact resistance affects the slow response of  $I_D$  vs  $V_{DS}$  in the measured output characteristics as shown in Fig. S11 of the supplementary material; thus, the drain current can be improved by lowering the contact resistance.

The drain current vs channel length at  $V_{GS} = 2$  V and  $V_{DS} = 5$  V is plotted in Fig. 3. The drain current is inversely proportional to the overall length of the channel except at the shortest channel length of 0.3  $\mu$ m, showing little degradation with respect to device scaling. The close agreement between the calculated field-effect mobility (with the effect of contact resistance included) and Hall mobility indicates that the deviation from linear behavior at the short channel length of 0.3  $\mu$ m in the inset of Fig. 3 is likely due to the contact resistance and not short channel effects such as velocity saturation. At a channel length of 0.3  $\mu$ m, the channel resistance is comparable to the contact resistance and the effective voltage applied to the channel is greatly diminished, lowering drain current. A lower resistance contact is expected to reduce the deviation evident in Fig. S11 (a) between the ideal square-law transistor model and actual TFT performance.

The interface trap charge density  $D_{it}$  can be calculated using<sup>31</sup>

$$S = \frac{kT\ln 10}{e} \left( 1 + \frac{e^2}{C_{\rm ox}} D_{\rm it} \right),$$

where *k*, *T*, and *e* are the Boltzmann constant, temperature, and electron charge, respectively. The calculated  $D_{it}$  is  $5.03 \times 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$ .

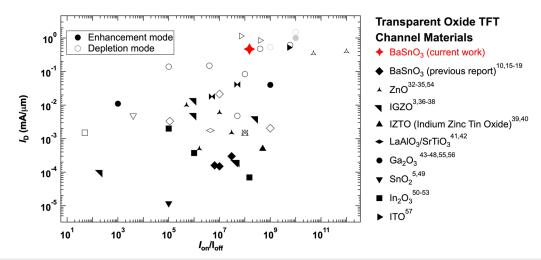

A comparison of the drain current vs on-off ratio among transparent oxide channel TFTs is shown in Fig. 4.<sup>3,5,10,15-19,32-57</sup> The high  $I_{\rm D}$  of the highest performance TFT with a transparent oxide channel was achieved on cleaved and transferred flakes of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> onto an opaque substrate;<sup>48</sup> this is not a scalable technology. These data are indicated as gray marks. Our BaSnO<sub>3</sub>-based TFT exhibits one of the best performances of all transparent oxide TFTs and is comparable to the best TFTs made with transparent oxide channel materials (in device structures in which other elements are not transparent). Its drain current is second best among all fully transparent scalable oxide channel TFTs.<sup>57</sup>

FIG. 4. Comparison of drain current in TFTs with transparent oxide channels with respect to the on/off current ratio. The drain current of the BaSnO<sub>3</sub> TFT described in this article is the highest value among all transparent oxide channel field-effect transistors. The solid symbols represent enhancement-mode TFT devices, and the hollow symbols represent depletion-mode TFT devices. The top right corner is the desired corner of the plot for the best TFT performance.

In summary, a fully transparent submicron TFT based on  $BaSnO_3$  has been fabricated with a high drain current and on/off current ratio. This breakthrough is made possible by (1) high mobility bare films in combination with (2) the development of a micrometer-scale etching method that preserves the surface roughness, conductivity, and mobility of  $BaSnO_3$  films. These results demonstrate the tremendous potential of  $BaSnO_3$  for the future of transparent electronics.

#### SUPPLEMENTARY MATERIAL

See the supplementary material for further data and discussion of the structural and electrical properties. This includes Xray diffraction  $\theta$ -2 $\theta$  and  $\phi$ -scans, a reflection high-energy electron diffraction (RHEED) intensity oscillation during the growth of a BaSnO<sub>3</sub> thin film, a reciprocal space map (RSM) of a BaSnO<sub>3</sub> thin film, atomic force microscope (AFM) images of the surface of a La-BaSnO<sub>3</sub> film before and after etching in dilute nitric acid, a plot of mobility vs carrier concentration for the La-BaSnO<sub>3</sub>/undoped BaSnO<sub>3</sub>/MgO heterostructures, a comparison of the 2-probe resistance of RIE-etched BaSnO3 and ion-milled BaSnO3 films following post annealing in flowing O2, the band diagram of the BaSnO3based TFT device fabricated with a HfO<sub>2</sub> gate dielectric and an ITO gate contact, the capacitance vs  $V_{GS}$  characteristics of an MOS ITO/ALD-grown HfO2/La-BaSnO3 capacitor, extraction of the contact resistance from the ITO/La-doped BaSnO<sub>3</sub>/ITO channel structure, analysis of the field-effect mobility that includes the high contact resistance, and a simulation of the ideal output characteristics of the BaSnO3-based FET.

#### ACKNOWLEDGMENTS

This material is based on work supported by the Air Force Office of Scientific Research under Award No. FA9550-16-1-0192 and from ASCENT, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA. H.P. acknowledges support from the National Science Foundation [Platform for the Accelerated Realization, Analysis, and Discovery of Interface Materials (PARADIM)] under Cooperative Agreement No. DMR-1539918. Substrate preparation was performed in part at the Cornell NanoScale Facility, a member of the National Nanotechnology Coordinated Infrastructure (NNCI), which is supported by the National Science Foundation (NSF, Grant No. ECCS-1542081). Material characterization made use of the shared facilities supported by NSF Grant No. MRI-1338010.

#### REFERENCES

- <sup>1</sup>G. Thomas, Nature 389, 907–908 (1997).

- <sup>2</sup> R. L. Hoffman, B. J. Norris, and J. F. Wager, Appl. Phys. Lett. 82, 733–735 (2003).

<sup>3</sup> K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono, Science 300, 1269–1272 (2003).

- <sup>4</sup>H. J. Kim, U. Kim, H. M. Kim, T. H. Kim, H. S. Mun, B.-G. Jeon, K. T. Hong, W.-J. Lee, C. Ju, K. H. Kim, and K. Char, Appl. Phys. Express 5, 061102 (2012).

<sup>5</sup>C. Ju, C. Park, H. Yang, U. Kim, Y. M. Kim, and K. Char, Curr. Appl. Phys. 16,

- 300–304 (2016).

- <sup>6</sup>H. Paik, Z. Chen, E. Lochocki, A. H. Seidner, A. Verma, N. Tanen, J. Park, M. Uchida, S. Shang, B.-C. Zhou, M. Brützam, R. Uecker, Z.-K. Liu, D. Jena, K. M. Shen, D. A. Muller, and D. G. Schlom, APL Mater. **5**, 116107 (2017).

- <sup>7</sup>H. Mizoguchi, H. W. Eng, and P. M. Woodward, Inorg. Chem. 43, 1667–1680 (2004).

- <sup>8</sup>P. Singh, B. J. Brandenburg, C. P. Sebastian, P. Singh, S. Singh, D. Kumar, and O. Parkash, Jpn. J. Appl. Phys., Part 1 47, 3540–3545 (2008).

- <sup>9</sup>K. Krishnaswamy, B. Himmetoglu, Y. Kang, A. Janotti, and C. G. Van de Walle, Phys. Rev. B **95**, 205202 (2017).

- <sup>10</sup>U. Kim, C. Park, T. Ha, Y. M. Kim, N. Kim, C. Ju, J. Park, J. You, J. H. Kim, and K. Char, APL Mater. **3**, 036101 (2015).

- <sup>11</sup>J. Yue, A. Prakash, M. C. Robbins, S. J. Koester, and B. Jalan, ACS Appl. Mater. Interfaces **10**, 21061–21065 (2018).

- <sup>12</sup>C. W. Schneider, S. Thiel, G. Hammerl, C. Richter, and J. Mannhart, Appl. Phys. Lett. 89, 122101 (2006).

- <sup>13</sup>D. M. Roessler and W. C. Walker, Phys. Rev. **159**, 733–738 (1967).

<sup>14</sup>J. Park, U. Kim, and K. Char, Appl. Phys. Lett. **108**, 092106 (2016).

<sup>15</sup>J. Shin, Y. M. Kim, Y. Kim, C. Park, and K. Char, Appl. Phys. Lett. **109**, 262102 (2016).

<sup>16</sup>C. Park, U. Kim, C. J. Ju, J. S. Park, Y. M. Kim, and K. Char, Appl. Phys. Lett. 105, 203503 (2014).

<sup>17</sup>Y. M. Kim, C. Park, T. Ha, U. Kim, N. Kim, J. Shin, Y. Kim, J. Yu, J. H. Kim, and K. Char, APL Mater. 5, 016104 (2017).

<sup>18</sup>Y. M. Kim, C. Park, U. Kim, C. Ju, and K. Char, Appl. Phys. Express 9, 011201 (2016).

<sup>19</sup>Y. Kim, Y. M. Kim, J. Shin, and K. Char, APL Mater. 6, 096104 (2018).

<sup>20</sup>H. Mun, U. Kim, H. M. Kim, C. Park, T. H. Kim, H. J. Kim, K. H. Kim, and K. Char, Appl. Phys. Lett. **102**, 252105 (2013).

<sup>21</sup> R. Uecker, R. Bertram, M. Brützam, Z. Galazka, T. M. Gesing, C. Guguschev, D. Klimm, M. Klupsch, A. Kwasniewski, and D. G. Schlom, J. Cryst. Growth 457, 137–142 (2017).

<sup>22</sup>C. Guguschev, D. Klimm, M. Brützam, T. M. Gesing, M. Gogolin, H. Paik, A. Dittmar, V. J. Fratello, and D. G. Schlom, J. Cryst. Growth **528**, 125263 (2019).

$^{23}$ C. Guguschev, D. Klimm, M. Brützam, T. M. Gesing, M. Gogolin, H. Paik, T. Markurt, D. J. Kok, A. Kwasniewski, U. Jendritzki, and D. G. Schlom, "Czochralski growth and characterization of perovskite-type (La, Nd)(Lu, Sc)O\_3 single crystals with a pseudocubic lattice parameter of 4.086 Å," J. Cryst. Growth (submitted).

<sup>24</sup>D. C. Look, C. E. Stutz, R. J. Molnar, K. Saarinen, and Z. Liliental-Weber, Solid State Commun. 117, 571–575 (2001).

<sup>25</sup>U. Kim, Ph.D. thesis, Seoul National University, 2015.

<sup>26</sup>S. Raghavan, T. Schumann, H. Kim, J. Y. Zhang, T. A. Cain, and S. Stemmer, APL Mater. 4, 016106 (2016).

<sup>27</sup> A. Prakash, P. Xu, A. Faghaninia, S. Shukla, J. W. Ager III, C. S. Lo, and B. Jalan, Nat. Commun. 8, 15167 (2017).

<sup>28</sup>J. Park, U.S. patent application 1126-051 (filed, December 6 2019).

<sup>29</sup>J. Park, U.S. patent application 1126-052 (filed, December 6 2019).

<sup>30</sup>E. Fortunato, P. Barquinha, and R. Martins, Adv. Mater. **24**, 2945–2986 (2012).

<sup>31</sup>W. L. Kalb and B. Batlogg, Phys. Rev. B 81, 035327 (2010).

<sup>32</sup>P. F. Carcia, R. S. McLean, M. H. Reilly, and G. Nunes, Jr., Appl. Phys. Lett. **82**, 1117–1119 (2003).

<sup>33</sup>H.-H. Hsieh and C.-C. Wu, Appl. Phys. Lett. **89**, 041109 (2006).

<sup>34</sup>B. Bayraktaroglu, K. Leedy, and R. Neidhard, <u>IEEE Electron Device Lett.</u> 30, 946–948 (2009).

<sup>35</sup>B.-Y. Oh, Y.-H. Kim, H.-J. Lee, B.-Y. Kim, H.-G. Park, J.-W. Han, G.-S. Heo, T.-W. Kim, K.-Y. Kim, and D.-S. Seo, Semicond. Sci. Technol. **26**, 085007 (2011).

<sup>36</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature 432, 488–492 (2004).

<sup>37</sup> R. Yao, Z. Zheng, M. Xiong, X. Zhang, X. Li, H. Ning, Z. Fang, W. Xie, X. Lu, and J. Peng, Appl. Phys. Lett. **112**, 103503 (2018).

<sup>38</sup>N. C. Su, S. J. Wang, and A. Chin, IEEE Electron Device Lett. **30**, 1317–1319 (2009).

<sup>39</sup>I. Noviyana, A. D. Lestari, M. Putri, M.-S. Won, J.-S. Bae, Y.-W. Heo, and H. Y. Lee, Materials **10**, 702 (2017).

<sup>40</sup>S. Tomai, M. Nishimura, M. Itose, M. Matuura, M. Kasami, S. Matsuzaki, H. Kawashima, F. Utsuno, and K. Yano, Jpn. J. Appl. Phys. **51**, 03CB01 (2012).

<sup>41</sup> R. Jany, C. Richter, C. Woltmann, G. Pfanzelt, B. Förg, M. Rommel, T. Reindl, U. Waizmann, J. Weis, J. A. Mundy, D. A. Muller, H. Boschker, and J. Mannhart, Adv. Mater. Interfaces 1, 1300031 (2014).

<sup>42</sup>L. Dong, Y. Q. Liu, M. Xu, Y. Q. Wu, R. Colby, E. A. Stach, R. Droopad, R. G. Gordon, and P. D. Ye, in *Proceedings of IEEE International Electron Devices Meeting* (IEEE, 2010), pp. 26.4.1–26.4.4.

<sup>43</sup> H. Zhou, K. Maize, G. Qiu, A. Shakouri, and P. D. Ye, Appl. Phys. Lett. 111, 092102 (2017).

<sup>44</sup>A. J. Green, K. D. Chabak, M. Baldini, N. Moser, R. Gilbert, R. C. Fitch, G. Wagner, Z. Galazka, J. McCandless, A. Crespo, K. Leedy, and G. H. Jessen, IEEE Electron Device Lett. **38**, 790–793 (2017).

<sup>45</sup>Z. Xia, C. Joishi, S. Krishnamoorthy, S. Bajaj, Y. Zhang, M. Brenner, S. Lodha, and S. Rajan, IEEE Electron Device Lett. **39**, 568–571 (2018).

<sup>46</sup>N. Moser, J. McCandless, A. Crespo, K. Leedy, A. Green, A. Neal, S. Mou, E. Ahmadi, J. Speck, K. Chabak, N. Peixoto, and G. Jessen, IEEE Electron Device Lett. 38, 775–778 (2017).

<sup>47</sup>K. D. Chabak, J. P. McCandless, N. A. Moser, A. J. Green, K. Mahalingam, A. Crespo, N. Hendricks, B. M. Howe, S. E. Tetlak, K. Leedy, R. C. Fitch, D. Wakimoto, K. Sasaki, A. Kuramata, and G. H. Jessen, IEEE Electron Device Lett. **39**, 67–70 (2018).

<sup>48</sup>H. Zhou, K. Maize, J. Noh, A. Shakouri, and P. D. Ye, ACS Omega **2**, 7723–7729 (2017).

<sup>49</sup>R. E. Presley, C. L. Munsee, C.-H. Park, D. Hong, J. F. Wager, and D. A. Keszler, J. Phys. D: Appl. Phys. **37**, 2810–2813 (2004).

<sup>50</sup>Z. Yuan, X. Zhu, X. Wang, X. Cai, B. Zhang, D. Qiu, and H. Wu, Thin Solid Films **519**, 3254–3258 (2011).

<sup>51</sup> P. K. Nayak, M. N. Hedhili, D. Cha, and H. N. Alshareef, Appl. Phys. Lett. **103**, 033518 (2013).

<sup>52</sup>N. Mitoma, S. Aikawa, X. Gao, T. Kizu, M. Shimizu, M.-F. Lin, T. Nabatame, and K. Tsukagoshi, Appl. Phys. Lett. **104**, 102103 (2014).

<sup>53</sup>L. Wang, M.-H. Yoon, G. Lu, Y. Yang, A. Facchetti, and T. J. Marks, Nat. Mater. 5, 893–900 (2006).

<sup>54</sup>B. Bayraktaroglu, K. Leedy, and R. Neidhard, IEEE Electron Device Lett. 29, 1024–1026 (2008).

<sup>55</sup>N. A. Moser, J. P. McCandless, A. Crespo, K. D. Leedy, A. J. Green, E. R. Heller, K. D. Chabak, N. Peixoto, and G. H. Jessen, Appl. Phys. Lett. **110**, 143505 (2017).

<sup>56</sup>W. S. Hwang, A. Verma, H. Peelaers, V. Protasenko, S. Rouvimov, H. Xing, A. Seabaugh, W. Haensch, C. Van de Walle, Z. Galazka, M. Albrecht, R. Fornari, and D. Jena, Appl. Phys. Lett. **104**, 203111 (2014).

<sup>57</sup>S. Li, M. Tian, Q. Gao, M. Wang, T. Li, Q. Hu, X. Li, and Y. Wu, Nat. Mater. 18, 1091–1097 (2019).