**IOHNS HOPKINS**

UNIVERSITY

<u>ش</u>

# Microwave Annealer for Dopant Activation in Silicon Chip

Cornell University

Joey Lin, MSE Department, Cornell University

#### Introduction

- Using 1 cm x 1 cm Si chip is common in experiment, and an annealer for Si chip is needed

- Conventionally, rapid thermal annealing (RTA) is used to activate dopants in semiconductors.

- Recently, microwave annealing (MWA) was found to be more efficient and stable than RTA [1].

- To make MWA more robust, a Si waveguide was designed to distribute microwave energy uniformly across the Si chip [2]

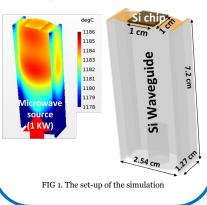

- This project evaluates uniformity of electric field and temperature by using the COMSOL multi-physics finite-element simulator with the setup shown in FIG 1.

## Results

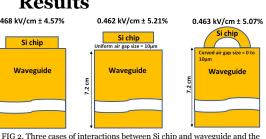

As shown in FIG 2. three possible interaction (No air gap, uniform air gap and curved air gap) between Si chip and waveguide were designed in simulation and electric field with variation was taken on top of the Si chip

The uniformity was good and the values were similar enough that anyone of the cases could be chosen as a representative

of the overall design.

m D D

2. Three cases of interactions between Si chip and waveguide and average electirc field across chip surface

- degC ..... ×103 1.18 1.18 1,180 °C ± 0.01% 0.25 1.18 1.18 0.47 kV/cm ± 4.6% across center across center area 1.18 area. 0.8 cm x 0.8 cm 0.25 1.18 0.8 cm x 0.8 cm 0.2 1.18 0.15 1.18 1.18 FIG 3. Electric and thermal field profile of the Si chip Standing wave peaks at surface **Epitaxial laver** 1 mm Si Electric field profile 0.2 in waveguide FIG 4. Design of epitaxial layer on Si chip and Electric field profile of the top Si waveguide with Si chip

- Because of an edge effect often occur at the edge of Si chip when manufactured, only the center 0.8 cm x 0.8 cm area is measured for both temperature and electric field as shown in FIG 3.

- As seen in the figures on the left, both electric field and temperature are unform and has small deviation across the chips surface, which is desirable

- Additional detail to the simulation was also added as shown in FIG 4.

- A thin 30 nm high-conductivity epitaxial layer was added to the top of the Si chip to examine the effect it will bring to the electric profile

- The effect to electric field was miniscule

#### Conclusion

- The variation of electric field was less than 7% across the center 0.8 cm x 0.8 cm area, while the variation of temperature was less than 0.1%

- Adding the high-conductivity Si epitaxial layer to the top was ineffective in changing the overall performance of the waveguide

- These results are promising, as we now know the waveguide design is valid to take on different alteration in the simulation while being able to maintain an uniform microwave effect on the Si chip

- Next step will be creating a physical prototype and conduct physical experiments to take measurements

#### Acknowledgement Jim Overhiser, Brenda Fisher and people who helped organizing

Jim Overhiser, Brenda Fisher and people who helped organizing the REU Prof. Darrell Schlom

Prof. James C. M. Hwang, Dr. Gianluca Fabi, Lei Li

### Reference

[1] C.-H. Tsai, C. P. Savant, M. Javad Asadi, Y.-M. Lin, I. Santos, Y.-H. Hsu, J. Kolwalski, L. Pelaz, W.-Y. Woon, C.-K. Lee, and J. C. M. Hwang, "Efficient and stable activation by microwave annealing of nanosheet silicon doped with phosphorus above its solubility limit," Appl. Phys. Lett., vol. 121, no. 5, p. 052103, Aug. 2022.

[2] J. C. M. Hwang, M. Javad Asadi, G. Fabi, and C. P. Savant, "Microwave annealer for semiconductor wafers," U.S. Patent Application No. 63/337,039, Apr. 29, 2022.

[3] J. C. M. Hwang, M. Javad Asadi, G. Fabi, and C. P. Savant, "Microwave annealer for semiconductor wafers," U.S. Patent Application No. 63/341,129, May 12, 2022.